#### Verifying RISC-V Vector and Bit Manipulation Extensions using STING Design Verification Tool

Shubhodeep Roy Choudhury, Shajid T, Jevin John, George S

## Agenda

- Vector and bit manipulation support Where we are?

- Overview of STING

- Verification strategy

- Results/Bugs Found

- Future work

## **Status of Vector and Bit Manipulation Support**

- Vector specification version 0.8-draft-20190906

- Bit manipulation specification version 0.9.2

- Support for all the 650+ vector and 100 bit manipulation instructions added to STING

- Work in progress

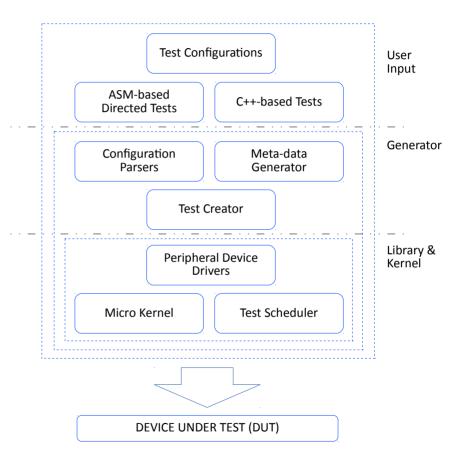

# **Overview of STING**

- Highly configurable and flexible bare metal program

- Intelligent and architecturally correct instruction sequences complete with results checking

- Supports constrained random, directed and, graph based test generation methodologies

- Portable stimulus simulations, emulation, FPGA or silicon

- MP and SoC ready

## **Stimulus Development Framework - Snippets**

- Programming framework for RISC-V test development

- High level language constructs mixed with inline assembly

- Allows reservation of registers, memory and hardware threads

- Enables users to install interrupt and exception handlers

- Embedded into the instruction stream after resolving the resource allocation constraints

- Easily integrate existing assembly and C/C++ tests

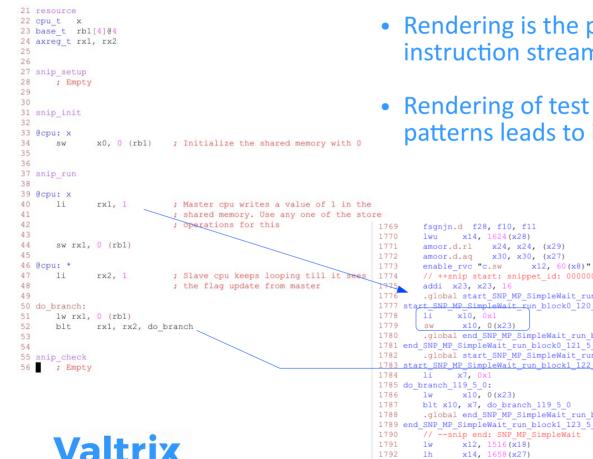

## **Rendering of Snippets**

en/tests/machine\_test

- Rendering is the process of embedding the snippet into instruction stream

- Rendering of test intent along with different stimulus patterns leads to increased cross product coverage

| £11                                 | 1601 // X26 <- [3101]                                                   |  |  |  |

|-------------------------------------|-------------------------------------------------------------------------|--|--|--|

| 8)                                  | 1602 lbu x24, 1053(x26)                                                 |  |  |  |

| 24, (x29)                           | 1603 fence r, io                                                        |  |  |  |

| 30, (x27)                           | 1604 enable_rvc "c.lw x14, 32(x15)"                                     |  |  |  |

| x12, 60(x8)"                        | 1605 sb x13, -1648(x29)                                                 |  |  |  |

| ppet_id: 00000005 SNP_MP_SimpleWait | 1606 fcvt.w.d x11, f11, rdn                                             |  |  |  |

|                                     | 1607 enable_rvc "c.ld x13, 72(x15)"                                     |  |  |  |

| _SimpleWait_run_block0_120_5_0      | 1608 enable_rvc "c.sw x13, 36(x15)"                                     |  |  |  |

| run_block0_120_5_0:                 | 1609 amominu.w.aq x5, x5, (x20)                                         |  |  |  |

|                                     | <pre>1610 // ++snip start: snippet_id: 01000005 SNP_MP_SimpleWait</pre> |  |  |  |

|                                     | 1611 addi x23, x23, 16                                                  |  |  |  |

| impleWait_run_block0_121_5_0        | <pre>1612 .global start_SNP_MP_SimpleWait_run_block1_122_5_1</pre>      |  |  |  |

| n_block0_121_5_0:                   | 1613 start_SNP_MP_SimpleWait_run_block1_122_5_1:                        |  |  |  |

| _SimpleWait_run_block1_122_5_0      | 1614 li x7, 0x1                                                         |  |  |  |

| run_block1_122_5_0:                 | 1615 do branch_119_5_1:                                                 |  |  |  |

|                                     | 1616 lw x5, 0(x23)                                                      |  |  |  |

|                                     | 1617 blt x5, x7, do_branch_119_5_1                                      |  |  |  |

|                                     | 1618 .global end_SNP_MP_SimpleWait_run_block1_123_5_1                   |  |  |  |

| ch_119_5_0                          | 1619 end_SNP_MP_SimpleWait_run_block1_123_5_1:                          |  |  |  |

| impleWait_run_block1_123_5_0        | 1620 //snip end: SNP_MP_SimpleWait                                      |  |  |  |

| n_block1_123_5_0:                   | 1621 amoor.d x6, x12, (x22)                                             |  |  |  |

| P_SimpleWait                        | 1622 1d x11, -2000(x22)                                                 |  |  |  |

| 8)                                  | 1623 enable_rvc "c.lw x14, 24(x15)"                                     |  |  |  |

| 7)                                  | 1624 amoadd.w.aq x14, x24, (x29)                                        |  |  |  |

| .s [+] 1752,5 7%                    | <pre>build/gen/tests/machine_test_l.s [+]</pre>                         |  |  |  |

# **Verification Strategy**

- Test plan based verification

- Pattern based tests Fixed and Random

- Constrained random and graph based test generation

- Snippets for directed scenarios

- Cross product with PMP, virtual memory, privilege mode of execution etc.

## **Fixed Pattern Directed Tests**

- Define data sets of fixed input and output patterns for every instruction

- Cover the corner case and interesting values

- Useful for basic testing of ISA implementation

| 1                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3 # VALTRIX TECHNOLOGIES PVT. LTD. CONFIDENTIAL<br>4 #                                                                                                                                                                                                                                                       |

| 4<br>5<br>6<br>7<br>8<br>9<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26 | <pre># VALTRIX TECHNOLOGIES PVT. LTD. CONFIDENTIAL # # # [2016] - Valtrix Technologies Private Limite # All Rights Reserved. # # NOTICE: All information contained herein # property of Valtrix Technologies Pvt. Lt1 # and technical concepts contained herein # Valtrix Technologies Pvt. Ltd. and may be # U.S. and Foreign Patents, patents in process # by trade secret or copyright law. Diss # information or reproduction of this mat # forbidden unless prior written permissic # Valtrix Technologies Pvt. Ltd. # # The dictionary given below defines the data# # SRC_1 contains the data to be loaded into tr # field defined in the dictionary. The expects</pre> | <pre>2 4 3 # VALTRIX TECHNOLOGIES PVT. LTD. CONFIDENTIAL 4 #</pre>                                                                                                                                                                                                                                           |

| 28<br>29                                                                                                                              | ISA CLZ CONF = I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33       { SRC_1 : 0x00000000UL       EXPECTED_RESULT : 0x00000020 },         34       { SRC_1 : 0x0100000UL       EXPECTED_RESULT : 0x00000007 },         35       { SRC_1 : 0x0010000UL       EXPECTED_RESULT : 0x0000000B },         46       { SRC 1 : 0x0010000UL       EXPECTED_RESULT : 0x0000000B }, |

| 30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>44                                                | DATA_SET : [<br>{ SRC_1 : 0xFFFFFFFFFFFFFFFFFFUL EXFF<br>{ SRC_1 : 0x0000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0 { SRC_1 : 0x0000001UL EXPECTED_RESULT : 0x0000001F },                                                                                                                                                                                                                                                      |

# **Fixed Pattern Directed Tests (contd)**

- Once data sets are ready, snippets are developed to program the input patterns and execute the instruction

- Results from the execution checkpointed and compared with the expected output

- Error reported in case a failure is is detected during comparison

21 ; Fixed pattern directed test for RV32B CLZ instruction 23 import "src/snippets/rv/rv param blocks.pb" 26 resource 27 cput x 28 base t rb1[8]@8 29 axreg t rx1, rx2 30 unum t rno = snp urandrange(0, ISA CLZ CONF.NUM DATA SET) 31 32 43 snip rur 33 snip setup 44 34 ; Empty 45 @cpu: x 46 35 47 for index in (0, ISA CLZ CONF.NUM DATA SET): 36 48 construct inst reg(inst = clz, imm = ISA CLZ CONF.DATA SET[index].SRC 1 37 snip init 49 reax = rx150 reav = rx238 51 reab = rb139 @cpu: x 52 write reg to mem (reg 53 40 check mem(val = ISA CLZ CONF.DATA SET[index].EXPECTED RESULT, 41 55 42 56 endfor 57 43 snip run 44 45 @cpu: x construct inst reg(inst = clz, imm = ISA CLZ CONF.DATA SET[rno].SRC 1, 46 47 reax = rx1,48 reav = rx2. 49 regb = rb1)50 51 52 snip check 53 54 @cpu: x 55 check mem (val = ISA CLZ CONF.DATA SET[rno].EXPECTED RESULT, 56

# **Fixed Pattern Directed Tests (contd)**

- In case of vectors, the data sets are tested with different configuration settings, which include

- Supported SEW values

- Supported LMUL values

- Different combinations of VSTART and VL

- Different combinations of mask register (V0)

- Different combinations of VLEN, ELEN, SLEN and SELEN

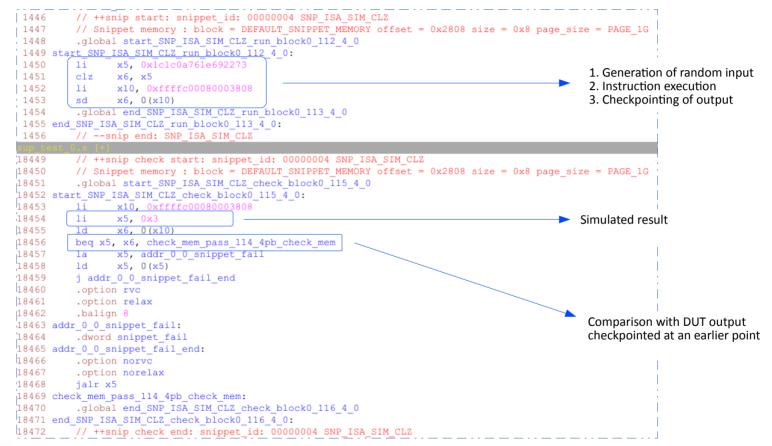

## **Random Pattern Directed Tests**

- Fixed pattern tests not adequate to test all input/source values

- Limitation addressed by random pattern tests, where randomly chosen values are programmed into the source register

- The expected output is simulated and compared with the result obtained from the DUT

| · · ·  |                                                                |

|--------|----------------------------------------------------------------|

|        | Random pattern directed test for RV32B CLZ instruction         |

| 3      |                                                                |

|        | port "src/snippets/rv/rv_param_blocks.pb"                      |

| 5      |                                                                |

|        | source                                                         |

| 7 cpi  |                                                                |

|        | im_t inp                                                       |

|        | im_t exp_res                                                   |

|        | reg_t rx1, rx2, rx3                                            |

|        | nory_t mem_chkp[8]@8                                           |

| 2      | n octum                                                        |

|        | p_setup<br>; Empty                                             |

| 4<br>5 | , millery                                                      |

|        | p init                                                         |

| 7      | "P_THITC                                                       |

|        | bu: x                                                          |

| 9 ,    |                                                                |

| o (    | inp = snp randnum()                                            |

|        |                                                                |

| 2      | la rx2, mem chkp                                               |

| 3      | write val to mem(regx = $rx1$ , regb = $rx2$ , val = 0)        |

| 4      |                                                                |

| 5 sni  | .p_run                                                         |

| 6      |                                                                |

| 7 @cp  | bu: x                                                          |

| 8      |                                                                |

| 9      | li rx1, inp                                                    |

| 0      |                                                                |

| 1      | clz rx2, rx1                                                   |

| 2      |                                                                |

| 3      | la rx3, mem_chkp                                               |

| 4      | <pre>write_reg_to_mem(regx = rx2, regb = rx3, offst = 0)</pre> |

| 5      |                                                                |

|        | p_check                                                        |

| 7      |                                                                |

|        | u: x                                                           |

| 9 7    | exp res = snp sim clz(inp)                                     |

| 0      |                                                                |

#### **Random Pattern Directed Tests (contd)**

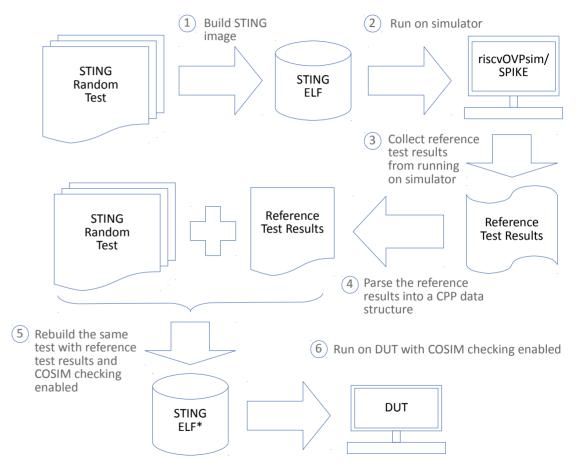

# **Random Tests with Checking**

- Pattern based tests are great spot checks but tend to add lot of noise in random tests

- Random tests for increased coverage and interaction with other elements

SYS1

• Correctness of test execution using cosim checking, multi pass results checking etc.

### **Random Tests with Checking (contd)**

| 8209       VSD.V V17, (x15)         8210       vssub.vv v19, v17, v16         8211       vsb.v v12, (x8)         8212       vlseg6hff.v v22, (x26)         8213       vsb.v v12, (x16)         8214       vlseg7e.v v7, (x16)         TEST – interleaved_vsb_v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 68<br>69<br>70<br>71<br>                                                                                                                 | vwmul.vv v24, v27, v21<br>vlhuff.v v10, (x18)<br>vslideup.vi v10, v4, 5<br>vmulhsu.vx v28, v30, x31<br>vlseg4eff.v v22, (x28), v0.t<br>vwmul.vv v18, v26, v21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 806<br>807<br>808<br>809<br>810                                                                       | vlseg4b.v v10, (x8)<br>vlseg4b.v v11, (x22), v0.t<br>vlseg4b.v v6, (x18)<br>vlseg4b.v v8, (x20), v0.t<br>vlseg4b.v v7, (x8)<br>TEST - only_vlseg4b_v                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8184       vlseg6bu.v v25, (x28), v0.t         8185       vsb.v v11, (x20)         8186       lwu       x31, -1592(x15)         8187       vsb.v v8, (x18)         8188       vlseg3b.v v20, (x28), x29, v0.t         8189       vsb.v v30, (x28), v0.t         8190       vlseg2hff.v v24, (x15)         8191       vsb.v v8, (x20)         8192       enable_rvc "c.sw       x10, 36(x8)"         8193       vsb.v v9, (x18), v0.t         8194       vlsseg6wu.v v22, (x28),x29, v0.t         8195       vsb.v v25, (x15)         8196       vlseg4hu.v v17, (x26)         8197       vsb.v v30, (x28), v0.t         8198       flw       f19, -1936(x28)         8199       vsb.v v30, (x28), v0.t         8200       vfsgnj.vf v14, v11, f1         8201       vsb.v v29, (x27), v0.t         8202       fsd       f15, -1992(x26)         8203       vsb.v v9, (x16), v0.t         8204       amoxor.w.rl       x24, x24, (x26)         8205       vsb.v v16, (x15)         8206       vfnmsub.vv v17, v16, v16         8207       vsb.v v4, (x22), v0.t         8208       vlxwu.v v6, (x20),v2, v0.t         8209 <t< td=""><td>2444<br/>45<br/>46<br/>47<br/>50<br/>51<br/>52<br/>53<br/>54<br/>55<br/>56<br/>57<br/>58<br/>59<br/>60<br/>61<br/>62<br/>63<br/>64<br/>65<br/>66<br/>66<br/>67</td><td><pre>srlw x7, x6, x7<br/>vwsubu.vx v24, v30, x14<br/>vlb.v v20, (x27), v0.t<br/>sb x25, -1607(x28)<br/>vwmul.vv v16, v30, v31<br/>vlseg3b.v v10, (x20)<br/>vwmul.vv v28, v19, v17<br/>vssseg4w.v v19, (x27), x29, v0.t<br/>fdiv.s f17, f22, f13, rdn<br/>enable_rvc "c.fld f12, 88(x15)"<br/>fclass.d x12, f5<br/>enable_rvc "c.sd x11, 104(x8)"<br/>vamoxore.v v17, v3, (x27), v17<br/>vlseg5bu.v v4, (x8)<br/>sw x31, 1792(x26)<br/>vwmul.vv v30, v27, v21<br/>vlseg2hu.v v7, (x16), v0.t<br/>enable_rvc "c.lw x14, 24(x15)"<br/>vsb.v v13, (x18)<br/>vwmul.vv v14, v4, v12<br/>vmmul.vv v14, v12, v10<br/>srliw x11, x10, 22<br/>vmmul.vv v28, v21, v18<br/>vmmaccsu.vv v10, v7, v5</pre></td><td>791<br/>792<br/>793<br/>794<br/>795<br/>796<br/>797<br/>798<br/>799<br/>800<br/>801<br/>802<br/>803<br/>804<br/>805</td><td><pre>vlseg4b.v v10, (x16) , v0.t<br/>vlseg4b.v v4, (x22)<br/>vlseg4b.v v25, (x28) , v0.t<br/>vlseg4b.v v10, (x22)<br/>vlseg4b.v v10, (x22)<br/>vlseg4b.v v5, (x16)<br/>vlseg4b.v v5, (x16)<br/>vlseg4b.v v4, (x22) , v0.t<br/>vlseg4b.v v4, (x22) , v0.t<br/>vlseg4b.v v4, (x20)<br/>vlseg4b.v v17, (x28) , v0.t<br/>vlseg4b.v v20, (x26)<br/>vlseg4b.v v27, (x28) , v0.t<br/>vlseg4b.v v22, (x26)<br/>vlseg4b.v v16, (x26)<br/>vlseg4b.v v28, (x28) , v0.t</pre></td></t<> | 2444<br>45<br>46<br>47<br>50<br>51<br>52<br>53<br>54<br>55<br>56<br>57<br>58<br>59<br>60<br>61<br>62<br>63<br>64<br>65<br>66<br>66<br>67 | <pre>srlw x7, x6, x7<br/>vwsubu.vx v24, v30, x14<br/>vlb.v v20, (x27), v0.t<br/>sb x25, -1607(x28)<br/>vwmul.vv v16, v30, v31<br/>vlseg3b.v v10, (x20)<br/>vwmul.vv v28, v19, v17<br/>vssseg4w.v v19, (x27), x29, v0.t<br/>fdiv.s f17, f22, f13, rdn<br/>enable_rvc "c.fld f12, 88(x15)"<br/>fclass.d x12, f5<br/>enable_rvc "c.sd x11, 104(x8)"<br/>vamoxore.v v17, v3, (x27), v17<br/>vlseg5bu.v v4, (x8)<br/>sw x31, 1792(x26)<br/>vwmul.vv v30, v27, v21<br/>vlseg2hu.v v7, (x16), v0.t<br/>enable_rvc "c.lw x14, 24(x15)"<br/>vsb.v v13, (x18)<br/>vwmul.vv v14, v4, v12<br/>vmmul.vv v14, v12, v10<br/>srliw x11, x10, 22<br/>vmmul.vv v28, v21, v18<br/>vmmaccsu.vv v10, v7, v5</pre> | 791<br>792<br>793<br>794<br>795<br>796<br>797<br>798<br>799<br>800<br>801<br>802<br>803<br>804<br>805 | <pre>vlseg4b.v v10, (x16) , v0.t<br/>vlseg4b.v v4, (x22)<br/>vlseg4b.v v25, (x28) , v0.t<br/>vlseg4b.v v10, (x22)<br/>vlseg4b.v v10, (x22)<br/>vlseg4b.v v5, (x16)<br/>vlseg4b.v v5, (x16)<br/>vlseg4b.v v4, (x22) , v0.t<br/>vlseg4b.v v4, (x22) , v0.t<br/>vlseg4b.v v4, (x20)<br/>vlseg4b.v v17, (x28) , v0.t<br/>vlseg4b.v v20, (x26)<br/>vlseg4b.v v27, (x28) , v0.t<br/>vlseg4b.v v22, (x26)<br/>vlseg4b.v v16, (x26)<br/>vlseg4b.v v28, (x28) , v0.t</pre> |

TEST – more\_vwmul\_vv

## **Miscellaneous Tests**

- Snippets developed for a large number of directed scenarios to check compliance with the specification

- Vector register overlap for widening/narrowing instructions and LMUL > 1

- Verifying if current SEW or LMUL is legal for the executing instruction

- Cross products with existing configurations for PMA, PMP, virtual memory, privileged mode of execution

- Configurations to generate different biased random sequences involving vector and bit manipulation instructions

# **Results/Bugs Found**

- Register overlap check failure for LMUL > 1

- Unexpected load/store address misaligned exceptions on randomizing SEW

- Incorrect decodes of several vector and bit-manipulation instructions

- No trap exception on executing vector atomics with unsupported SEW setting

- Unexpected VL setting at the end of vector fault-only-first load instructions

- Violation of rules in setting VL due to randomization of SEW and AVL

- Incorrect results with vector arithmetic operations

- Irregularities in sign extension of result of vector atomic operations

- Unexpected output of saturating arithmetic instructions on randomization of vector rounding mode (VXRM)

- VXRM/VXSAT not part of FCSR

### **Future Work**

- Add support for the changes introduced by newer revisions of specification

- Improved LMUL randomization

- Handle different random combinations of striping length (SLEN)

- Enhance STING coverage manager for vector and bit manipulation instructions

- Tests for Vector EDIV extension